# **RX7 Stimulator Base Station**

## **RX7** Overview

The RX7 base station is a high performance processor available with either two or five 100 MHz, 1600 MFLOPS Sharc DSPs. You can use the base station's onboard DSPs to design and generate complex arbitrary waveforms or complex patterns of biphasic pulses in real-time. The RX7 has been developed specifically for microstimulation applications. As part of TDT's RX7G MicroStimulator system, the RX7's primary role is to control the MS16 stimulus isolator, transferring hardware control and stimulation information across fiber optics. This proven digital communication system optically isolates the RX7 from the electrical stimulator, eliminating AC power surges and noise. For more information see "MS4/MS16 Stimulus Isolator" on page 8-31.

The RX7 includes 40 bits of digital I/O, analog output, and can include one or two fiber optic input ports for acquisition of digitized data from Medusa preamplifiers. Acquired signals can be filtered, rectified, or smoothed for stimulus output or dynamic real-time stimulus control based on analog control signals from virtually any signal source.

### **Power and Communication**

The RX7 mounts in a System 3 zBus Powered Device Chassis (ZB1PS) and communicates with the PC using the Optibit (PO5/FO5) PC interface. The ZB1PS is UL compliant, see the ZB1PS Operations Manual for power and safety information.

### Software Control

Software control is implemented with circuit files developed using TDT's RP Visual Design Studio (RPvdsEx). Circuits are loaded to the processor through TDT runtime applications or custom applications. This manual includes device specific information needed during circuit design. For circuit design techniques and a complete reference of the RPvdsEx circuit components, see the *RPvdsEx Manual*.

3-36 System 3

# **RX Architecture**

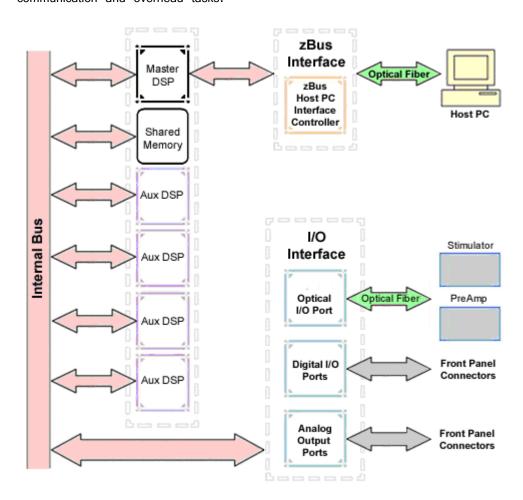

Each RX multiprocessor device is equipped with either two or five digital signal processors (DSPs). The multi-DSP architecture allows processing tasks to be distributed across multiple processors and enables data to be transferred to the PC quickly and efficiently. The DSPs include one master and one or four auxiliary DSP(s). 128 MB SDRAM of system memory is shared by all DSPs. When designing circuits the maximum number of components for each RX DSP is 256.

Each DSP communicates with an internal bus to send and receive information from the I/O controller and the shared memory. The master DSP supervises overall system boot up and operation. The master DSP also acts as the main data interface between the zBus (host PC) and the multi-DSP environment.

Because the zBus communicates only with the master processor, these devices operate most efficiently when the circuit related processing tasks assigned to the master DSP are minimized, allowing more processor power (cycles) for communication and overhead tasks.

The RX7 contains two DB25 connectors for interfacing with 40 bits of digital I/O and 4 channels of analog output. A BNC connector is provided for access to the first analog output channel. One or two fiber optic Medusa preamp ports enable connections for up to 32 channels of analog input.

### **Distributing Data Across DSPs**

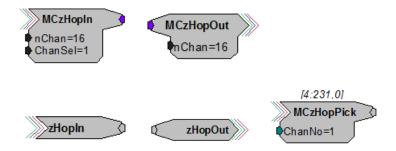

In RPvdsEx data can be transferred between each of the auxiliary DSPs as well as the master DSP using zHop components.

Components such as MCzHopIn and MCzHopOut can be used for multi-channel signals while components such as zHopIn, zHopOut, and MCzHopPick are used with single-channel signals. Up to 126 pairs can be used in a single RPvdsEx circuit.

#### **Bus Related Delays**

The zHop Bus introduces a single sample delay. However, this delay is taken care of for the user in OpenEx when Timing and Data Saving macros are used.

See "MultiProcessor Circuit Design" in the *RPvdsEx Manual* for these and other multiprocessor circuit design techniques.

# **RX7** Features

## **DSP Status Displays**

All high performance RX multiprocessors include status lights and a display screen to report the status of the individual processors.

#### **Status Lights**

Up to five LEDs report the status of the multiprocessor's individual DSPs. When the device is turned on, they will glow steadily. If the demands on a DSP exceed 99% of its capacity on any given cycle, the corresponding LED will flash very rapidly ( $\sim$ 3 times per second).

#### **Front Panel Display Screen**

3-38 System 3

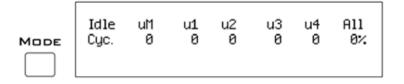

The front panel display screen reports detailed information about the status of the system. The display includes two lines. The top line reports the system mode, Run! or Idle, and displays heading labels for the second line. The second line reports the user's choice of status indicators for each DSP followed by an aggregate value.

The user can cycle through the various status indicators using the Mode button to the left of the display. Push and release the button to change the display or push and hold the button for one second then release to automatically cycle through each of the display options. The display screen may also report system status such as booting status (Booting DSP) or alert the user when the device's microcode needs to be reprogrammed (Firmware Blank).

#### **Status Indicators**

Cyc: cycle usage

Ovr: processor cycle overages

Bus%: percentage of internal device's bus capacity used

I/O%: percentage of data transfer capacity used

Important!

The status lights will flash (~3 times a second) to alert the user when a device goes over the cycle usage limit, even if only for a particular cycle. This helps to identify periodic overages caused by components in time slices.

### **Fiber Optic Output Port (Stimulator)**

The output port, labeled Stimulator, can be used to transfer microstimulation waveforms to the MS16/MS4 Stimulus Isolator and/or to control its digital output. See the "MS4/MS16 Stimulus Isolator" on page 8-31.

Important!

This fiber optic port is disabled if the sampling rate of the system is set to a value greater than  $\sim$ 25 kHz.

## Fiber Optic Input Ports (Amp-A and Amp-B)

The RX7 base station can acquire digitized signals from a Medusa preamplifier over a fiber optic cable. This provides loss-less signal acquisition between the amplifier and the base station. Up to two fiber optic ports are provided to support simultaneous acquisition from up to two preamplifiers. Each port can input up to 16 channels at a maximum sampling rate of  $\sim 25$  kHz. The fiber optic ports provide oversampling. See "Fiber Oversampling", below for more information.

The fiber optic ports can be used with any of the Medusa preamplifiers including the RA16PA, RA4PA, or RA8GA. The channel numbers for each port begin at a fixed offset regardless of the number of channels available on the connected device.

#### Channels are numbered as follows:

Amp-B 1 - 16 Amp-B 17 - 32

#### Fiber Oversampling (acquisition only)

The fiber optic cable that carries the signals to the fiber optic input ports on the RX7 has a transfer rate limitation of 6.25 Mbits/s. With 16 channels of data and 16 bits per sample, this limitation translates to a maximum sampling rate of  $\sim 25$  kHz.

However, the need may arise to run a circuit at a higher sampling rate while still acquiring data via a fiber optic port. The first two fiber optic ports on an RX device can oversample the digitized signals that have already been sampled up to 4X or ~100 kHz. This will allow an RX7 to run a DSP chain at ~50 kHz or ~100 kHz, and still sample data acquired through an optically connected preamplifier that digitized the incoming data stream at its maximum rate of ~25 kHz.

Oversampling is performed on the base station. The signals being acquired will still be sampled at  $\sim$ 25 kHz on the preamplifier. This means that, even with oversampling, signals acquired by an optically connected preamplifier are still governed by the bandwidth and frequency response of the preamplifier.

When acquiring up to 16 channels of data on the first fiber optic input port of the RX7, the signals will be oversampled 4X to  $\sim$ 100 kHz. If the RX7 is equipped with a second fiber optic input port and data is being acquired on both ports, the signals on second port will be oversampled 2X to  $\sim$ 50 kHz.

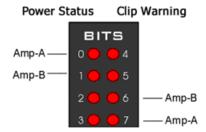

# **Amp Status and Clip Warning Lights**

Amp lights are located to the right of each fiber optic port. These lights are used to indicate the power status or provide a clip warning for the connected amplifiers.

When an amplifier is not connected the Amp light will flash in a slow steady pattern. The light is lit when the amplifier is connected and begins to flash quickly when the voltage on the battery for the corresponding amplifier is low. When any channel on the connected amplifier produces a voltage approaching the maximum input of the amplifier, the corresponding light will flash rapidly to warn that clipping may occur if the signal exceeds the maximum input voltage. See the corresponding preamplifier section for more information on input range and clip warnings.

Important!

The Li-ion batteries voltage decreases rapidly once the battery low light is on. Data acquisition will suffer if the battery is not charged soon after the light goes on.

#### **Amplifier Status Patterns**

| Light Pattern                          | Amplifier Status       |  |  |

|----------------------------------------|------------------------|--|--|

| Solid                                  | Connected              |  |  |

| Very slow flash (~1 every two seconds) | Not connected          |  |  |

| Slow flash (~1 per second)             | Connected and charging |  |  |

| Rapid flash                            | Battery low            |  |  |

| Very rapid flash                       | Clip Warning           |  |  |

Note:

If the amplifier appears to be connected and the amplifier status light is flashing slowly, check to ensure that the device is connected properly.

## **Bits Lights**

The RX7's eight Bits lights are user configurable. By default the Bits lights indicate the logic level (light when high) for the eight bit-addressable digital I/O lines. The Bits lights can also be configured to provide information about amplifier status or act as logic level lights for any of the other four bytes of digital I/O.

3-40 System 3

#### Using the Bits Lights to Display Amplifier Status

Note: Because clip warning and amplifier status are always displayed using the Amp lights (located directly to the right of each fiber optic port), TDT recommends using the Bits lights for other applications. See "Amp Status and Clip Warning Lights" on page 3-39, for more information.

When the Bits lights are configured to display the amplifier status, the left column of lights indicates the power status and the right column indicates a clip warning for the corresponding amplifier.

"Amplifier Status Patterns" on page 3-39 shows the light pattern and corresponding amplifier status for the power status lights (0 - 3). Clip lights flash very rapidly when any channel on the connected amplifier produces a voltage approaching the maximum input of the amplifier.

### **Analog Output**

The RX7 is equipped with four channels of 16-bit PCM D/A. The sampling rate is user selectable up to a maximum of ~100 kHz. The D/A is DC coupled and has a built-in upsampler for improved audio playback. The upsampler is controlled through one of the RX7's programmable bits and can be turned off to allow the D/A to drive external devices such as a stimulator. Channel one analog output can be accessed via a front Panel BNC (DAC-1). All four analog channels can be accessed via the DB25 Multi I/O connector (pins 14 - 17).

Important!

When using the RX7 with the stimulus isolator, the sampling rate set for this device cannot exceed  $\sim$ 25 kHz—a limitation of the fiber optic connection between the RX7 and the stimulus isolator.

# Digital I/O

The RX7 base station has 40 digital I/O lines. Eight bits are bit-addressable. The remaining 32 bits are four word-addressable bytes. Digital I/O lines are accessed via the two 25-pin connectors on the front of the RX7. See the "Digital I/O Circuit Design" section of the *RPvdsEx Manual* for more information on programming the digital I/O.

CAUTION!: The first eight bits of bit-addressable digital I/O on RX devices are unbuffered. When used as inputs, overvoltages on these lines can cause severe damage to the system. TDT recommends when sending digital signals into the device, never send a signal with amplitude greater than five volts into any digital input.

#### Configuring the Programmable I/O Lines

Each of the eight bit-addressable lines can be independently configured as inputs or outputs. The digital I/O lines can be configured as inputs or outputs in groups of eight bits – that is as byte A, byte B, byte C, and byte D. Note, however, that the bytes must be addressed as if part of a word, not as individual bytes. See "Addressing Digital Bits In A Word" in the *RPvdsEx Manual* for more information.

By default, all bits are configured as inputs. This default setting is intended to prevent damage to equipment that might be connected to the digital I/O lines. The user can configure the bits in the RPvdsEx configuration register. The configuration register is also used to determine what the eight front panel Bits lights represent.

#### To access the bit configuration register:

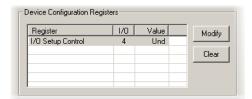

- 1. Click the Device Setup command on the Implement menu.

- In the Set Hardware Parameters dialog box, click the Device Type box and select the RX7 Elec-Stimulator from the list.

The dialog expands to display the Device Configuration Register.

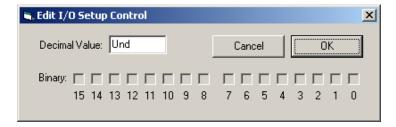

3. Click Modify to display the Edit I/O Setup Control dialog box.

In this dialog box, a series of check boxes are used to create a bitmask that is used to program all bits.

- 4. To enable the check boxes, delete Und from the Decimal Value box.

- 5. To determine the desired value, select or clear the check boxes according to the table below. By default, all check boxes are cleared (value = 0). Selecting a check box sets the corresponding bit in the bitmask to one.

- 6. When the configuration is complete, click **OK** to return to the **Set Hardware Parameters** dialog box.

| Bit # | Description                                                                                                                                                                                                                                  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0-7   | Each of these bits controls the configuration of one of the eight addressable bits as inputs or outputs. Setting the bit to one will configure that bit as an output.                                                                        |  |  |  |  |

| 8-11  | Each of these bits controls the configuration of one of the four addressable bytes as inputs or outputs. Setting the bit to one will configure that byte as an output.  bit 8 - byte A, bit 9 - byte B, bit 10 - byte C, and bit 11 - byte D |  |  |  |  |

| 12-14 | Create a bit code that determines how the front panel Bits lights are used, see table below.                                                                                                                                                 |  |  |  |  |

3-42 System 3

| Bit # | Description                                            |  |  |  |  |

|-------|--------------------------------------------------------|--|--|--|--|

| 15    | Setting the bit to one will disable the D/A upsampler. |  |  |  |  |

### Bit Codes for Controlling the Bit Lights (Boxes 12-14)

By default, check boxes 12 -14 in the Edit I/O Setup Control dialog box (previous diagram) are cleared to create the bit code 000. This configures the eight front panel Bits lights to act as activity lights (glow when high) for the eight bit addressable digital I/O lines. The Bits lights can also be configured to provide information about amplifier status or act as activity lights for any of the other four bytes of digital I/O.

| Bit Flags                | Bits set to 1 | Bit Lights Used For                                |

|--------------------------|---------------|----------------------------------------------------|

| 000                      | None          | Logical level lights for bit-addressable I/O lines |

| 010                      | 13            | Amplifier Clip Warning/Power Status display        |

| 100 F F F F 12           | 14            | Enable logical level lights for byte A             |

| 101<br>                  | 12, 14        | Enable logical level lights for byte B             |

| 110<br>F F T<br>14 13 12 | 13, 14        | Enable logical level lights for byte C             |

| 111<br>                  | 12, 13, 14    | Enable logical level lights for byte D             |

### **XLink**

The XLink is not supported at this time.

# **RX7 Technical Specifications**

The RX7 is designed for use with the MS16 stimulus isolator. The RX7 is also equipped with a fiber optic input port for use with Medusa or Adjustable Gain preamplifiers.

**Note:** Specifications for the stimulus isolator D/As and the preamplifiers A/D are found under the technical specifications for those devices.

| DSP                                                                             | 100 MHz Sharc ADSP 21161, 600 MFLOPS Peak<br>Two or Five                                |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Memory                                                                          | 128 MB SDRAM (Shared)                                                                   |

| D/A                                                                             | 4 channels, 16-bit PCM                                                                  |

| Sample Rate                                                                     | Up to 97.65625 kHz (8X upsampled to 200 kHz default operation)*                         |

| Frequency Response                                                              | DC - Nyquist (~1/2 sample rate)                                                         |

| Voltage Out                                                                     | +/- 10.0 Volts                                                                          |

| Voltage Out Accuracy                                                            | +/- 10%                                                                                 |

| S/N (typical)                                                                   | 84 dB (20 Hz to 25 KHz)<br>82 dB with upsampling disabled                               |

| THD (typical) -77 dB for 1 kHz output at 5 Vrms -74 dB with upsampling disabled |                                                                                         |

| Output Impedance                                                                | 10 Ohm                                                                                  |

| Fiber Optic Ports                                                               | One or Two Inputs, Output for Stimulator *                                              |

| Digital I/O                                                                     | 40 bits programmable (8 bits bit-addressable and a 32 bit word, addressable as 4 bytes) |

<sup>\*</sup> Note: When used with the microstimulator, the sampling rate is limited to 24.414 kHz by the Stimulator Fiber Optic Port.

Note: zBus chasis (ZB1PS) required for power and communication.

3-44 System 3

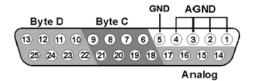

# **DB25 Connector Pinouts**

### Multi I/O

| Pin | Name       | Description                                             | Pin | Name       | Description                                            |

|-----|------------|---------------------------------------------------------|-----|------------|--------------------------------------------------------|

| 1   | AGND       | Analog Ground                                           | 14  | A1         | Analog Output Channels                                 |

| 2   |            |                                                         | 15  | A2         |                                                        |

| 3   |            |                                                         | 16  | <b>A</b> 3 |                                                        |

| 4   |            |                                                         | 17  | A4         |                                                        |

| 5   | GND        | Digital I/O Ground                                      | 18  | C0         | Byte C                                                 |

| 6   | C1         | Byte C Word addressable digital I/O Bits 1, 3, 5, and 7 | 19  | C2         | Word addressable<br>digital I/O<br>Bits 0, 2, 4, and 6 |

| 7   | <b>C</b> 3 |                                                         | 20  | C4         |                                                        |

| 8   | <b>C</b> 5 |                                                         | 21  | C6         |                                                        |

| 9   | C7         |                                                         | 22  | D0         | Byte D                                                 |

| 10  | D1         | Byte D Word addressable digital I/O Bits 1, 3, 5, and 7 | 23  | D2         | Word addressable digital I/O Bits 0, 2, 4, and 6       |

| 11  | D3         |                                                         | 24  | D4         |                                                        |

| 12  | D5         |                                                         | 25  | D6         |                                                        |

| 13  | D7         |                                                         |     |            |                                                        |

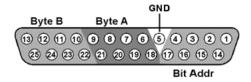

### Digital I/O

| Pin | Name       | Description                                |  | Pin | Name       | Description                                      |

|-----|------------|--------------------------------------------|--|-----|------------|--------------------------------------------------|

| 1   | BA0        | Bit Addressable digital I/O                |  | 14  | BA1        | Bit Addressable digital I/O                      |

| 2   | BA2        | Bits 0, 2, 4, and 6                        |  | 15  | BA3        | Bits 1, 3, 5, and 7                              |

| 3   | BA4        |                                            |  | 16  | BA5        |                                                  |

| 4   | BA6        |                                            |  | 17  | BA7        |                                                  |

| 5   | GND        | Digital I/O Ground                         |  | 18  | <b>A</b> 0 | Byte A                                           |

| 6   | A1         | Byte A<br>Word addressable digital I/<br>O |  | 19  | A2         | Word addressable digital I/C Bits 0, 2, 4, and 6 |

| 7   | A3         |                                            |  | 20  | A4         | Bits 0, 2, 4, and 6                              |

| 8   | <b>A</b> 5 | Bits 1, 3, 5, and 7                        |  | 21  | A6         |                                                  |

| 9   | A7         |                                            |  | 22  | В0         | Byte B                                           |

| 10  | B1         | Byte B<br>Word addressable digital I/      |  | 23  | B2         | Word addressable digital I/O Bits 0, 2, 4, and 6 |

| 11  | В3         |                                            |  | 24  | B4         | Dits 0, 2, 4, ditu 6                             |

| 12  | B5         | Bits 1, 3, 5, and 7                        |  | 25  | В6         |                                                  |

| 13  | B7         |                                            |  |     |            |                                                  |